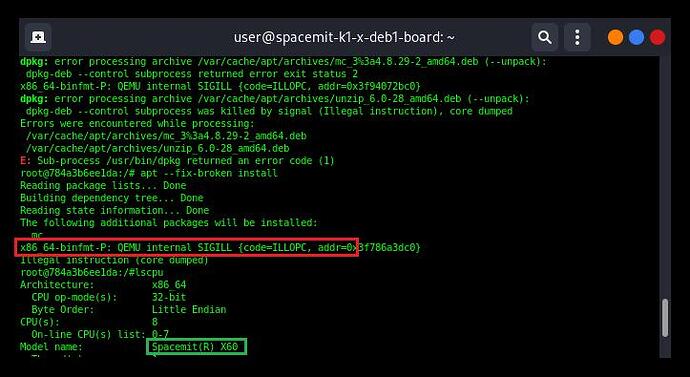

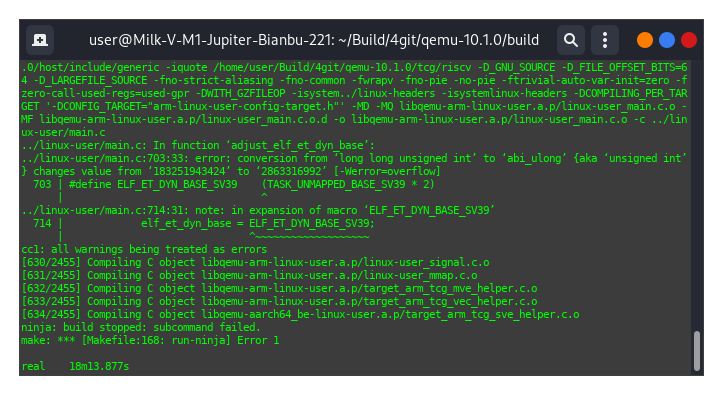

I think I’ve fixed this issue—it stems from a problem in QEMU’s common code. Based on my analysis, the vsetvl instruction hardcodes the use of the t6 register, which overwrites other data and causes the error. Perhaps you could apply the follow patch to the QEMU source code and compile it to test.

I can’t upload a pre-built qemu-x86_64 binary on this forum. If you need it, please leave your email address, and I’ll send it to you directly.

Maybe you can try the follow steps to build qemu from source code in spacemit-k1 board.

mkdir build-qemu-x86

../configure --target-list=x86_64-linux-user --static --disable-system

make

My patch to fix the issue.

diff --git a/tcg/riscv/tcg-target.c.inc b/tcg/riscv/tcg-target.c.inc

index 31b9f7d87a..26acc69064 100644

--- a/tcg/riscv/tcg-target.c.inc

+++ b/tcg/riscv/tcg-target.c.inc

@@ -3022,10 +3022,10 @@ static void probe_frac_lmul_1(TCGType type, MemOp vsew)

p->vset_insn = encode_vseti(OPC_VSETIVLI, TCG_REG_ZERO, avl, vtype);

} else if (lmul_eq_avl) {

/* rd != 0 and rs1 == 0 uses vlmax */

- p->vset_insn = encode_vset(OPC_VSETVLI, TCG_REG_TMP0, TCG_REG_ZERO, vtype);

+ p->vset_insn = encode_vset(OPC_VSETVLI, TCG_REG_TMP3, TCG_REG_ZERO, vtype);

} else {

- p->movi_insn = encode_i(OPC_ADDI, TCG_REG_TMP0, TCG_REG_ZERO, avl);

- p->vset_insn = encode_vset(OPC_VSETVLI, TCG_REG_ZERO, TCG_REG_TMP0, vtype);

+ p->movi_insn = encode_i(OPC_ADDI, TCG_REG_TMP3, TCG_REG_ZERO, avl);

+ p->vset_insn = encode_vset(OPC_VSETVLI, TCG_REG_ZERO, TCG_REG_TMP3, vtype);

}

}

@@ -3070,6 +3070,8 @@ static void tcg_target_init(TCGContext *s)

tcg_regset_set_reg(s->reserved_regs, TCG_REG_TP);

if (cpuinfo & CPUINFO_ZVE64X) {

+ tcg_regset_set_reg(s->reserved_regs, TCG_REG_TMP3);

+

switch (riscv_lg2_vlenb) {

case TCG_TYPE_V64:

tcg_target_available_regs[TCG_TYPE_V64] = ALL_VECTOR_REGS;

diff --git a/tcg/riscv/tcg-target.h b/tcg/riscv/tcg-target.h

index 6dc77d944b..0f2dced8e2 100644

--- a/tcg/riscv/tcg-target.h

+++ b/tcg/riscv/tcg-target.h

@@ -55,6 +55,7 @@ typedef enum {

TCG_REG_TMP0 = TCG_REG_T6,

TCG_REG_TMP1 = TCG_REG_T5,

TCG_REG_TMP2 = TCG_REG_T4,

+ TCG_REG_TMP3 = TCG_REG_T3,

} TCGReg;

#define TCG_REG_ZERO TCG_REG_ZERO