接下来我们来看一下RISC-V的安全架构。

RISC-V PMP/ePMP based TEE

RISC-V在特权架构上和Arm v8/9架构有非常相似之处, RISC-V特权级架构如下:

- 用户态(U 态):运行一般的用户应用程序,具有最低的特权级别,只能访问有限的指令和资源,对硬件的直接访问受到严格限制,以防止用户程序对系统造成破坏。

- 内核态(S 态和 H 态):S 态用于操作系统的内核或监督程序。H 态则用于 Hypervisor,负责虚拟机的运行和管理。

- 机器模式(M 态):具有最高的特权级别,可执行M态特权级指令,运行特权级固件(如OpenSBI), 提供特权级服务,类似Arm v8/v9的EL3或者Root 态。

前面我们已经了解了TrustZone的实现原理,TrustZone Extension在特权架构上增加了EL3,用于运行特权固件(如TF-A), 而RISC-V 在诞生之初就拥有比S/H态更高的特权级模式M态,所以RISC-V 也完全可以像TrustZone一样实现物理核(Hart)的虚拟化。

不同的是,TrustZone只能虚拟出2个世界,而RISC-V则没有这方面的限制,RISC-V可以在特权固件(OpenSBI)的管理下,能更像创建进程一样创建出任意多的虚拟”世界“(数量依赖与系统资源)。

每一个”世界“RISC-V通常称之为Domain, vCPU(这里借用CPU虚拟化中的虚拟CPU的概念,本质上是一样的)是物理CPU在每个Domain中运行时的抽象,本质上是一个物理CPU在不同Domain之间分时运行,而安全固件(增加了Domain管理功能的特权固件)则提供了Domain之间的上下文管理和切换。

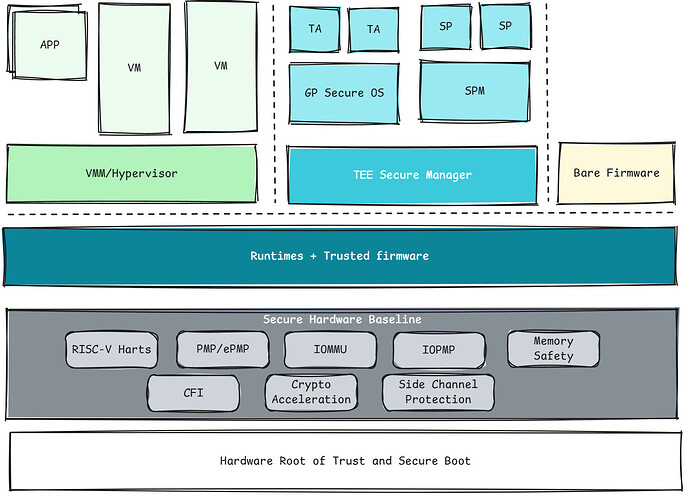

我们仍然可以按照理解操作系统管理应用程序或者Hypervisor管理虚拟机的方式来理解安全固件对Domain的管理,于是RSIC-V可以实现如下的软件整体架构:

RISC-V Generic Software Architecture with TEE Enabled

上图展示RISC-V"虚拟"出多个Domain来实现TEE架构的软件参考模型,但最关键的是RISC-V如何解决不同Domain之间的隔离问题。所谓隔离,从技术上看就是如何实现权限管理和访问控制。我们仍然通过用户态和内核态的隔离来举例,因为用户态和内核态的隔离大家都比较熟悉,而且不同CPU架构之间都大同小异。

用户态和内核态的隔离是通过内存管理单元(MMU)来实现的。MMU 的主要功能是将虚拟地址转换为物理地址,并对访问进行权限检查。在操作系统中,用户态和内核态运行在不同的虚拟地址空间,操作系统内核可以通过管理MMU 页表来控制不同特权下对物理内存的访问权限,从而实现两者的隔离。

- 用户态页表:用户态程序使用的页表只包含用户程序可以访问的物理内存区域的映射。这些区域通常是用户程序的代码、数据和栈等。用户态页表中的映射项会设置相应的访问权限,一般只允许用户态程序进行读、写和执行操作,并且不允许访问内核空间的物理内存。

- 内核态页表:内核态使用的页表包含了整个系统的物理内存映射,不仅包括用户程序的内存区域,还包括内核代码、内核数据结构和设备内存等。内核态页表中的映射项权限设置更为灵活,内核可以根据需要进行各种操作,如对硬件设备的直接访问等。

每个应用程序都有自己独立的页表,每个页表包含了应用程序完整的用户空间。当操作系统从一个应用程序切换到另一个应用程序时,操作系统主要做的其中一个事儿就是进行页表切换。

应用程序地址空间是通过MMU来管理的,那RSIC-V domain的地址空间是通过什么来管理的呢?这就是RISC-V架构特有的物理内存保护(PMP)模块。

RISC-V PMP (Physical Memory Protection)

RISC-V 物理内存保护(Physical Memory Protection,PMP)是 RISC-V 特权架构的重要组成部分,在硬件层面提供灵活且细粒度的内存访问控制。它允许操作系统或监督程序依据实际需求,对不同物理内存区域设置各异的访问权限,以此防止低特权级(U, H/S)程序进行非法的内存访问操作,增强系统安全性和稳定性。简单地讲, PMP是一个轻量级的MPU, 它基于实地址(MMU是虚地址)模式对低特权等级的程序提供地址空间访问的权限管理, 而M模式并不受PMP的影响(除非把PMP的表项锁住,具体细节不展开介绍)。

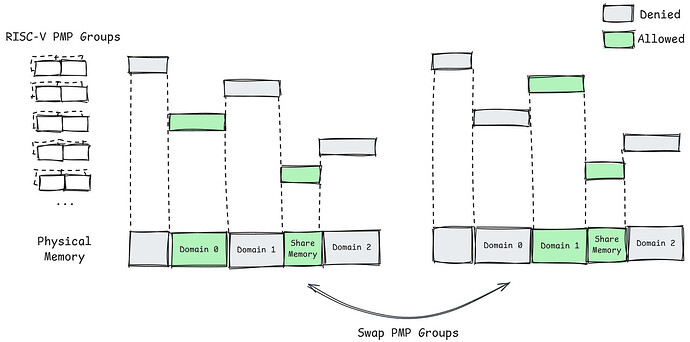

PMP只允许M模式下的特权固件对它进行编程(MMU是受S态的Kernel管理),M态固件可以像操作系统内核维护MMU页表一样来维护PMP的表项,从而实现不同Domain之间访问权限的切换(类似MMU页表切换)。基于PMP实现多个Domain访问隔离的机制如下图所示:

RISC-V Memory Isolations Using PMP Swapping

RISC-V SUM (Supervisor User Memory)

在早期的操作系统内存管理机制中,用户空间和内核空间虽然在概念上有所区分,但在实际的内存使用和访问控制方面存在一定的漏洞。用户程序可以在用户空间分配内存,并且这些内存可以被标记为可执行。

攻击者利用这一特性,通过精心构造的攻击代码,将恶意代码注入到用户空间的可执行内存中。当系统因某些操作进入内核模式后,攻击者可以诱导内核跳转到这些恶意代码所在的用户空间内存区域并执行,从而实现提权攻击,获取系统的最高权限,进而控制整个系统。这种攻击方式严重威胁到系统的安全性和稳定性。

同时,仅仅禁止内核模式下执行用户空间代码已经不足以保障系统的安全。在一些情况下,即使内核不执行用户空间的代码,但如果可以随意访问用户空间的内存,仍然可能被攻击者利用。例如,攻击者可以通过操纵用户空间的内存数据,诱导内核在访问这些数据时执行不安全的操作,从而绕过其他安全机制。

为了抵御这种类型的攻击,SMEP(Supervisor Mode Execution Protection)和 SMAP(Supervisor Mode Access Prevention)机制应运而生。SMEP 的核心思想是在内核模式下禁止执行用户空间的代码。当内核尝试执行位于用户空间的指令时,SMEP 会触发异常,阻止恶意代码的执行,从而大大增强了系统对提权攻击的抵抗能力;SMAP 进一步限制了内核模式下对用户空间内存的访问,当内核尝试在没有明确授权的情况下访问用户空间的内存时,SMAP 会触发异常,阻止这种不安全的访问操作,从而进一步增强了系统的安全性。

RISC-V SUM(Supervisor User Memory) bit 是 RISC-V 架构中用于增强内存访问控制安全性的一种机制,内核态程序对用户态内存的访问会受到严格限制。当SUM=0时,内核态只能访问自身的内存区域,而无法直接访问用户态的内存。这就确保了用户态内存数据的隔离性和安全性,防止内核态代码意外或恶意地访问用户态数据,即使内核态具有较高的特权级别, 从而为系统提供SMAP保护能力。

RISC-V ePMP (Enhanced Physical Memory Protection)

前面说到PMP主要作用于U、S/H等特权级,而M态是不受PMP约束的(Lock模式这种特殊场景我们暂且不讨论),过高的权限往往会带来安全上隐患。RISC-V ePMP (Enhanced Physical Memory Protection)增强型物理内存保护是对传统 RISC-V PMP(Physical Memory Protection,物理内存保护)机制的扩展和增强,旨在提供更强大、更灵活的内存访问控制, 提供对M模式SMEP和SMAP的保护能力。

RISC-V ePMP SMEP/SMAP Protection

RISC-V I/O Physical Memory Protection

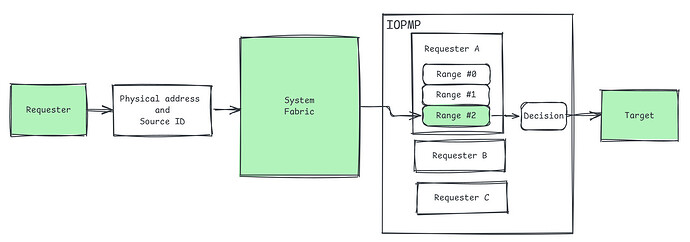

上一章节介绍了RISC-V基于PMP/ePMP的物理地址空间访问的保护机制, 但PMP/ePMP是RISC-V特权架构的一部分,是用来约束CPU对物理内存、MMIO的访问权限的,但RISC-V又是如何对DMA master设备进行访问控制的呢?这就要说到RISC-V IOPMP(Input/Output Physical Memory Protection)这个RISC-V Non-ISA 扩展了。

IOPMP 和PMP/ePMPl类似,本质上是一种物理内存保护机制,只不过它聚焦于 DMA设备的访问控制。相比与PMP,IOPMP的实现会更加复杂,因为它需要考量同时来自不同设备的访问请求,同时也还要做到低时延。IOPMP也提供了类似PMP的访问权限配置表,能够允许安全固件配置针对不同设备对物理地址空间的访问设置特定的访问权限,确保I/O设备只允许访问授权的物理地址空间。

RISC-V IOPMP Reference Model

IOPMP也不仅仅用来保护DMA外设的物理地址空间访问,它也可以作用于CPU。这种情况下, IOPMP往往会部署在slave侧,但由于RISC-V系统里的RV CPU已经有PMP/ePMP保护了, 所以一般会将IOPMP对RV CPU的访问配置成直通方式(Bypass)。部署在slave侧的IOPMP就和Arm上的TZASC IP非常相似了,差别在于TZASC是基于NS信号来进行访问控制,而IOPMP是基于Source ID (或者叫Reqester ID), 也就是TZASC是把设备分成Group(安全和非安全), 而IOPMP则可以为每个设备单独配置权限,提供了更加细粒度的权限管控。

以上便是RISC-V 架构实现可惜执行环境所提供的核心组件。我们再简单对比一下RISC-V 安全架构和Arm TrustZone的差别。

TrustZone的核心思想是将资源划分成安全"世界"和非安全”世界“,并通过NS位进行标记,资源的访问控制主要集中在slave侧的安全IP,只能采用slave端防护策略,不同的slave(如内存控制器、ROM/SRAM控制器、MMIO等)采用不同的安全IP(TZASC、TZMA、TZPC、AXI2APB Bridge等), 安全IP基于NS信号进行权限管控。

而RISC-V在架构上并没有2个”世界“的限制,理论上可以虚拟出任意数目的Domain, Domain隔离所提供的安全IP(也就是PMP和IOPMP)都是基于地址空间的权限管控(TrustZone是基于NS信号),管控策略更加灵活。

其中PMP采用master端(核内)防护策略,而IOPMP既可采用master端防护策略也可以采用slave端防护策略,甚至采用混合方式的防护策略,IOPMP部署方式可以灵活多样,并且不需要像TrustZone那样,不同的slave设备采用不同的安全IP,RISC-V完全可以采用同一个IOPMP IP(但允许不同的配置,比如entry表项的数目)。但总的来说,RISC-V和Arm在实现TEE隔离机制上是殊途同归。

进迭时空 V100 TEE 扩展

进迭时空 V100 AI CPU原型除了实现了上述基于RISC-V架构的TEE 标准组件(PMP/ePMP、IOPMP)以外,还实现了基于HSM(Hardware Security Module)的硬件信任根(HW RoT), 并基于此信任根实现了整个AI CPU系统的安全启动、安全调试,旨在构建和提供完整的TEE软硬件系统和TEE解决方案。

HSM(Hardware Security Module)

V100 AI CPU集成了HSM硬件安全模块,旨在提供密码与安全功能。HSM能够实现密钥管理(密钥的生成、存储和处理)、安全启动、数据加密解密等一系列密码相关的功能,以及提供物理防护、安全传感器等安全保障机制,能够隔离外部恶意软件的攻击。HSM可以用于构建、验证可靠的软件,以保护在软件加载并初次访问之前的安全启动。HSM包含有加密/解密硬件加速功能, 和软件解决方案相比能够有效降低CPU负载并提高密码学运算的安全性。

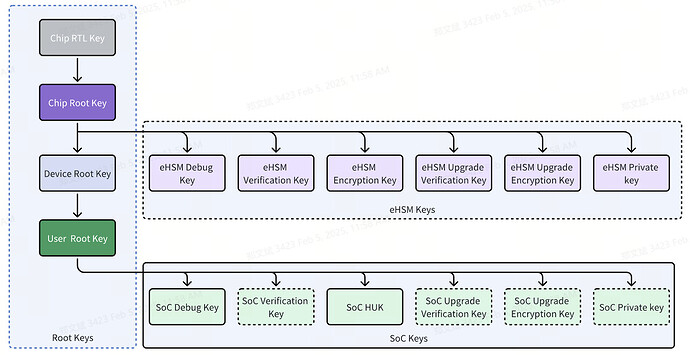

根密钥作为整个硬件信任根(HW RoT)的基础,其密钥的安全性是整个安全子系统的核心考量。本方案使用HSM作为系统的RoT,密钥存储在OTP中,需要保证其机密性和完整性,同时需要严格管理密钥的访问和使用权限。加密后的密钥及其属性、CRC校验码均存储在OTP中,HSM硬件自动读取并校验CRC后,通过专用的SKE解密模块对密钥进行解密,并存储在KMU中以供后续使用。

HSM Key Management Overview

安全启动

安全启动主要提供以下功能:

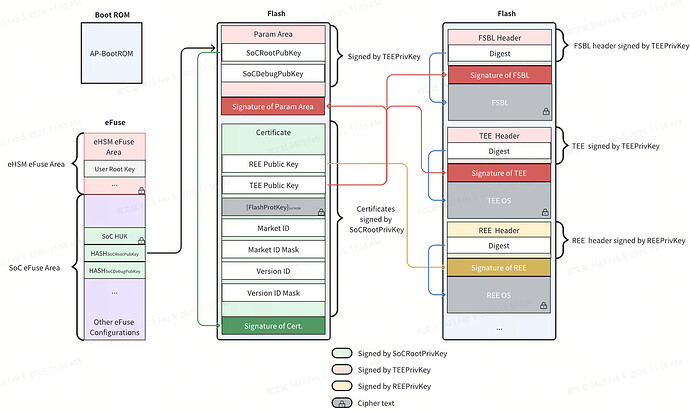

安全启动机制

- 信任根RoT: OTP加密存储芯片唯一密钥(HUK), 支持客户根秘钥

- 信任链CoT: 通过ROT逐级验签, 实现信任链传递

安全启动组件

- HSM: 国密二级认证安全岛, 提供秘钥的安全存储、派生和使用、国际(RSA/ECC/AES/DES/SHA等)、国密(SM2/3/4等)密码算法引擎

- RMU子系统: 从BootROM到Bootloader到Firmware的安全启动

ROM安全启动流程

- 使用根公钥(Root Public Key)对Cerfiticates进行验签, 用HUK对加密密钥进行解密

- 参数段验签并传递参数

- 下一跳代码镜像解密

- 下一条代码镜像验签

- 传递Certfiticates并跳转到下一跳启动固件(FSBL)

ROM安全启动信任链

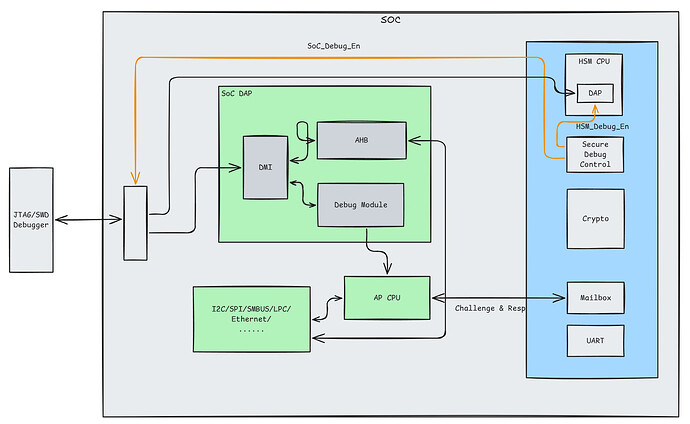

安全调试

当芯片/设备进入产品阶段, 也就是安全功能被激活之后,调试功能将会被关闭或者授权开启。HSM支持安全调试授权认证,只有通过认证之后,调试才允许被开启。安全调试的授权认证支持非对称或对称算法。

安全调试的授权认证流程如下:

- 主机通过 UART 或邮箱向 eHSM 发送调试请求

- HSM 向主机发送challenge(UID + 随机数)

- 主机使用调试密钥对challenge进行签名,并发返回给HSM(a) 非对称:使用 hsm/ap 调试密钥的相应私钥进行签名(b) 对称:使用 hsm/ap 调试密钥计算 CMAC 值

- HSM 使用 hsm/ap 调试密钥验证其签名

- 如果验证通过,HSM启用 hsm/ap 调试端口。

基于HSM实现AI CPU安全调试

TEE 软件架构

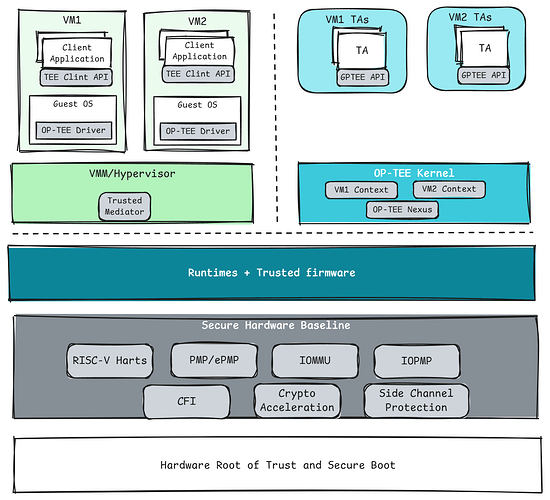

OP-TEE(Open Portable Trusted Execution Environment)是一个开源的可信执行环境(TEE)软件实现框架,它利用 ARM TrustZone 等硬件隔离技术(OP-TEE 早期专门为TrustZone设计实现,目前也已经支持RISC-V架构),将设备的运行环境分为安全世界(Secure World)和普通世界(Normal World)。

普通世界运行主操作系统,如 Linux、Android 等;安全世界则用于运行 OP-TEE 及执行敏感任务,确保安全世界中的应用程序和数据不受普通世界的干扰。OP-TEE支持 GlobalPlatform TEE 国际标准,保证与其他遵循同一标准的应用和服务能无缝协作,提高了其通用性和互操作性, 相比其他的TEE OS,OP-TEE目前支持几十种SoC板级,具有更好的软件生态。

而 OP-TEE Virtualization 是指 OP-TEE 具备对虚拟机场景的支持,允许TEE世界在不创建多个虚拟机运行多个TEE OS的情况下,使一个 OP-TEE 实例就能够服务于多个REE虚拟机各自的可信应用(TA)。进迭V100 支持CPU虚拟化,目前采用OP-TEE作为TEE OS,既能满足平台虚拟化的要求,也能很好地融入OP-TEE的软件生态,降低用户开发和学习成本。

基于OP-TEE 实现虚拟机场景的TEE整体软件框架

参考资料:

[1] "Building a Secure System using TrustZone® Technology " https://documentation-service.arm.com/static/5f212796500e883ab8e74531

[2] "Intel® TDX Connect Architecture Specification " https://cdrdv2-public.intel.com/773614/intel-tdx-connect-architecture-specification.pdf

[3] "Intel® Trust Domain CPU Architectural Extensions " https://cdrdv2-public.intel.com/733582/intel-tdx-cpu-architectural-specification.pdf

[4] “Intel(R) Software Guard Extensions Developer Guide” https://cdrdv2-public.intel.com/671334/intel-sgx-developer-guide.pdf

[5] “Learn the architecture - TrustZone for AArch64.” Documentation – Arm Developer

[6] https://www.cvedetails.com/

[7] https://optee.readthedocs.io/en/latest/

[8] "RISC-V CVM Extension: Confidential Virtual Machine for RISC-V " https://docs.google.com/document/d/1ME7THEF9JWuFqwm75x586y3wzhPeXahK8keLcgjZYG8/edit?tab=t.0

[9] "Penai-Enclave " https://penglai-doc.readthedocs.io/en/latest